集成电路产业通常被分为芯片设计、芯片制造、封装测试三大领域。其中,芯片制造是集成电路产业门槛行业,高端芯片制造的玩家越来越少,目前只剩下台积电(TSMC)、三星(SAMSUNG)和英特尔(Intel)三家了。随着先进封装技术的发展,芯片制造和封装测试逐渐融合。我们惊奇地发现,在先进封装领域的高端玩家,竟然也是台积电、三星、英特尔三家,而传统的封测厂商,已经被他们远远地抛在身后。那么,这三家的先进封装到底有什么独到之处呢?他们为何能超越传统封测厂商,先进封装产业,我们通过三期文章来解读三家的先进封装技术。今天,我们详细解读台积电的先进封装技术。

今天,在高端芯片制造领域,台积电独占鳌头,在先进封装领域,台积电依然稳居前1。

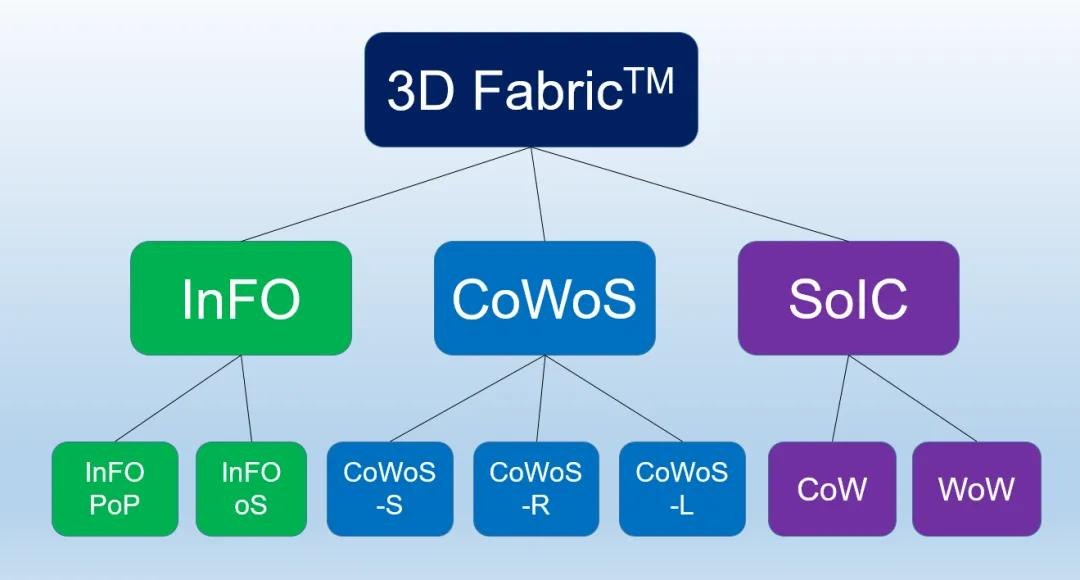

台积电的先进封装称为3D Fabric,并为此专门注册了商标,因此,我们看到的3D Fabric会有TM上标,意为Trade Mark。

3D Fabric被分为三大类:InFO,CoWoS和SoIC。

其中InFO分为InFO_PoP和InFO_oS两类,CoWoS分为CoWoS-S,CoWoS-R,CoWoS-L三类,SoIC分为CoW和WoW两类,如下图所示:

1 InFO

InFO全称为Integrated Fan-Out,集成扇出技术。要了解InFO,我们先了解Fan-Out。

Fan-Out扇出型封装技术

随着芯片技术的发展,芯片功能越来越丰富,晶体管数量越来越多,芯片的引脚也越来越多,密度也越来越大,传统的封装技术已经难以满足要求。

传统的芯片引脚都是排列在芯片的周边,呈线阵排列,需要较大的芯片面积才能安放更多的芯片引脚,并且这种位于芯片边沿的线阵引脚排列仅适合键合线连接,限制了芯片技术的发展。

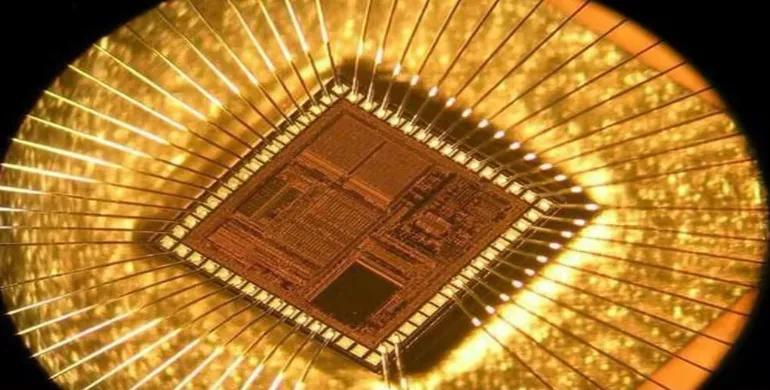

下图所示为传统的键合线芯片封装,芯片引脚位于芯片边沿,通过键合线和基板相连。键合线通常采用高纯度黄金制成,线径有18微米,25微米不等,成本很高,互连密度也难以提升。

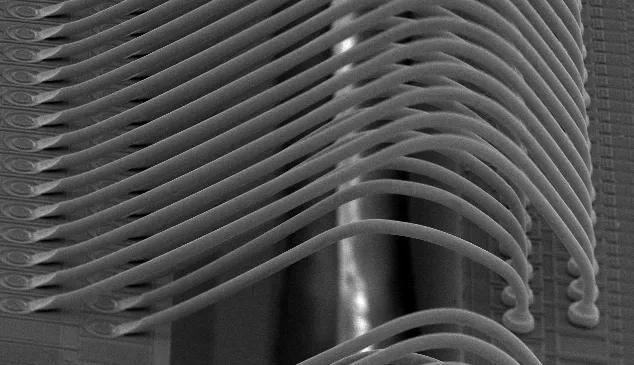

为了有效利用芯片边沿的空间,提高引脚的密度,增加电气连接,有的芯片引脚设计为两列或者多列,需要两层或者多层键合线,这样键合线设计就会变得复杂,线间距很近,和线径相当,容易出现搭接现象,对可靠性带来了挑战,如下图所示。

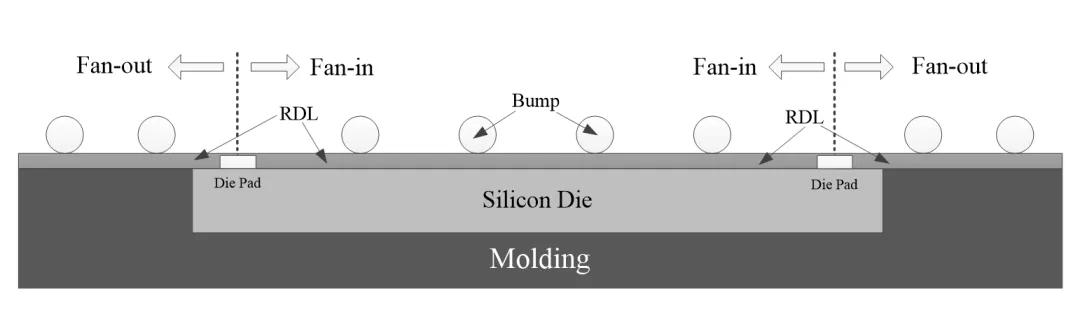

为了适应芯片技术的快速发展以及方便后续的封装,需要将原来设计的芯片引脚位置,通过晶圆级金属重新布线(RDL)和凸点(Bump)改变其引脚位置,使芯片能适用于不同的封装形式。

根据重新分布的凸点位置不同,可分为扇入型(Fan-in)和扇出型(Fan-out)两种,扇入型RDL是指RDL Bump位于芯片本体之上,扇出型RDL则是指RDL Bump位于芯片外的Molding之上,如下图所示:

通过Fan-out和Fan-in技术:①可改变芯片Die Pad原有的设计,增加原有设计的附加价值;②可加大I/O的间距,提供较大的凸块面积,降低基板与元件间的应力,增加元件的可靠性;③将引脚以面阵列分布,支持更多的引脚数量;④代替部分IC线路设计,加速IC开发时间。

随着芯片对更多I/O要求的提高,传统Bond Wire封装不能有效支持上千I/O的芯片,采用重新布线层(RDL)将I/O焊盘重新分配到凸点焊盘,改变芯片原有的I/O焊盘布局,在这些设计中重新布线层可能非常拥挤,需要采用多个RDL层才可能完成所有布线。

Fan-in技术由于受芯片本身面积的限制,单独应用的比较少,绝大多数都是和Fan-out技术一起应用,或者二者兼而有之,逐渐Fan-Out就成了此类封装的代名词,现在人们提及Fan-Out,通常就涵盖了Fan-in和Fan-Out。

Fan-Out通常是以整个晶圆的形式进行封装,称为Fan-out Wafer Level Package(FOWLP)是Wafer Level Package(WLP)的一种,因此我们需要先了解Wafer Level Package晶圆级封装技术。

WLP晶圆级封装技术

在WLP技术出现之前,传统封装的工艺步骤主要在裸片切割分片后进行。先对晶圆(Wafer)进行切割分片(Dicing),然后再封装(Packaging)成各种形式。

晶圆级封装WLP于2000年左右问世,和传统封装不同,在封装过程中大部分工艺过程都是对晶圆进行操作,即在晶圆上进行整体封装,封装完成后再进行切割分片。

一开始,WLP多采用Fan-in型态,主要应用于面积较小、引脚数量少的芯片。随着IC工艺的提升,芯片面积缩小,芯片面积内无法容纳足够的引脚数量,因此衍生出Fan-Out WLP封装形态,实现在芯片面积范围外充分利用RDL做连接,以获取更多的引脚数。

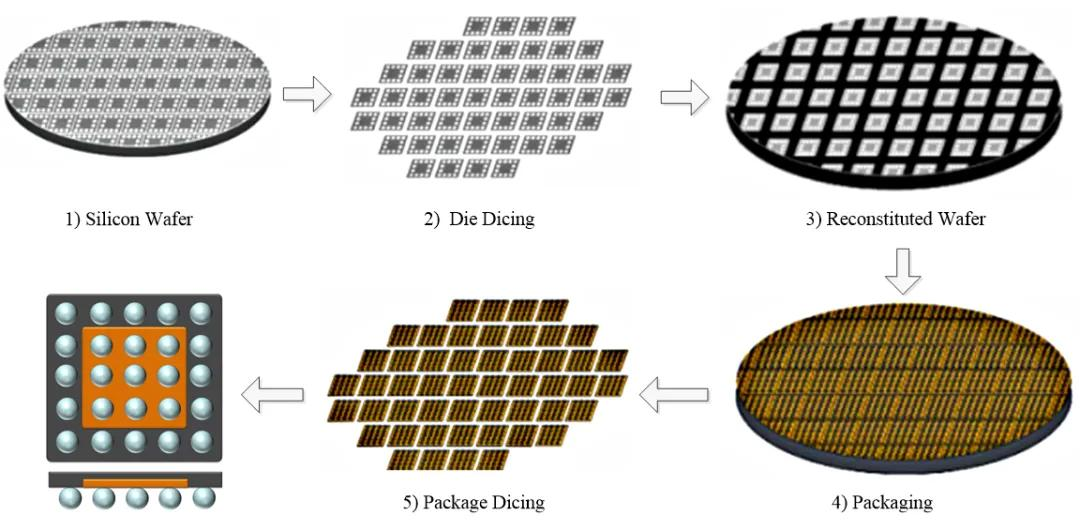

由于要将RDL和Bump引出到裸芯片的外围,因此需要先进行裸芯片晶圆的划片分割,然后将独立的裸芯片重新配置到载体晶圆中,并以此为基础,通过批量处理、金属化布线互连,形成封装。其封装流程如下图所示。

如今,Fan-out Wafer Level Package已经成为主流。由于采用批量封装,整个晶圆能够实现一次全部封装,封装效率比传统封装有很大提升,此外,成本的降低也是WLP晶圆级封装的另一个推动力量。

INFO

InFO(Integrated Fan-out)是台积电于2017年开发出来的一种FOWLP先进封装技术,是在FOWLP工艺上的集成,可以理解为多个芯片Fan-Out工艺的集成,而FOWLP则偏重于Fan-Out封装工艺本身,一般多是单芯片封装。

InFO通过Fan-out技术集成了多个芯片,具备多芯片集成的空间,应用灵活,可应用于射频和无线芯片的封装,处理器和基带芯片封装,图形处理器和网络芯片的封装。

苹果iPhone处理器早年一直是三星生产,但台积电却从苹果A11开始,接连拿下iPhone处理器订单,关键之一,就在于台积电的InFO技术,能让芯片与芯片在封装内直接互连,减少体积,腾出宝贵的空间给电池或其他零件使用。苹果从iPhone 7就开始采用InFO封装,后续持续在用,包括其他品牌的手机也开始普遍使用这个技术。苹果和台积电的加入改变了先进封装技术的应用状况,使市场逐渐接受并普遍应用InFO先进封装技术。

InFO是一种创新的晶圆级系统集成技术平台,具有高密度RDL(重新分布层)和TIV(通过InFO通孔)的特点,可实现高密度互连和性能,适用于移动、高性能计算等各种应用。InFO平台提供针对特定应用进行优化的各种封装方案。

根据InFO封装的结构,台积电将其分为InFO_PoP和InFO_oS。

InFO_PoP

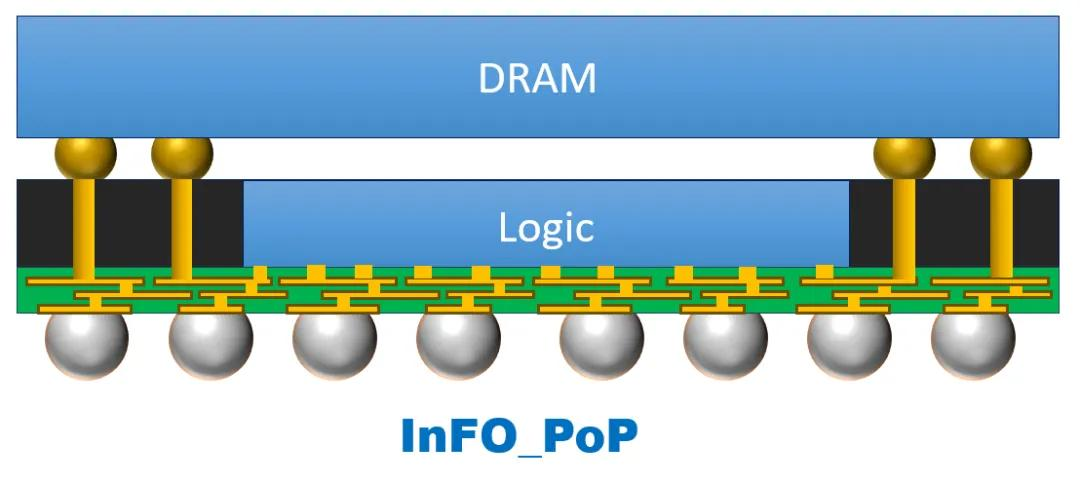

InFO_PoP号称3D晶圆级扇出型封装,和传统意义上的3D封装并不相同,严格来说属于2D+,我们后面讲到的SoIC才是3D封装。

InFO_PoP采用高密度RDL和TIV(Through InFO Via)将芯片引脚引到外围形成面阵,然后采用PoP(Package on Package)将上下芯片连接到一起,可集成移动AP和DRAM封装堆叠,适用于移动应用。与FC_PoP相比,InFO_PoP无有机基板和C4凸块而具有更薄的外形和更好的电气和热性能。

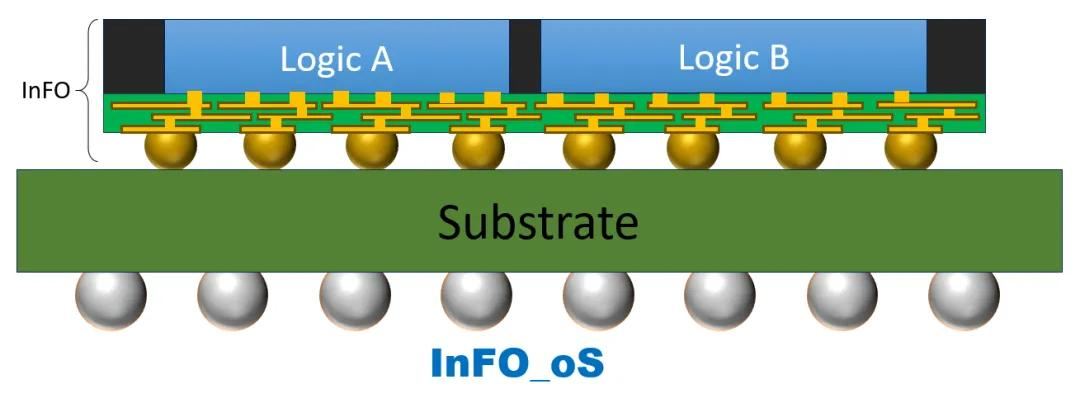

InFO_oS

InFO_oS,其中oS的含义为on Substrate,两个或者多个芯片通过InFO工艺进行集成,然后再安装在基板上,如下图所示。

利用InFO高密度互连技术,可支持2/2µm RDL线宽/间距,可集成多个先进逻辑芯片,支持SoC上的混合焊盘间距,最小I/O间距为40µm,最小C4凸块间距为130µm。

2 CoWoS

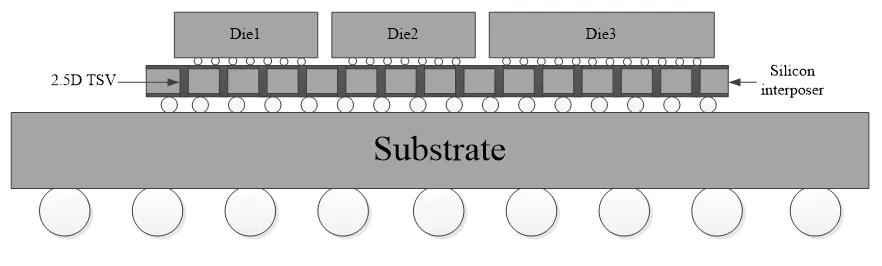

CoWoS(

Chip-on-Wafer-on-Substrate)是台积电推出的2.5D封装技术,CoWoS是把芯片封装到硅转接板Silicon Interposer(中介层)上,并使用硅转接板上的高密度布线进行互连,然后再安装在封装基板上,如下图所示。

CoWoS和前面讲到的InFO都是台积电首先创造的,CoWoS有硅转接板Silicon Interposer,InFO则没有。CoWoS针对市场,连线数量和封装尺寸都比较大。InFO针对性价比市场,封装尺寸较小,连线数量也比较少。

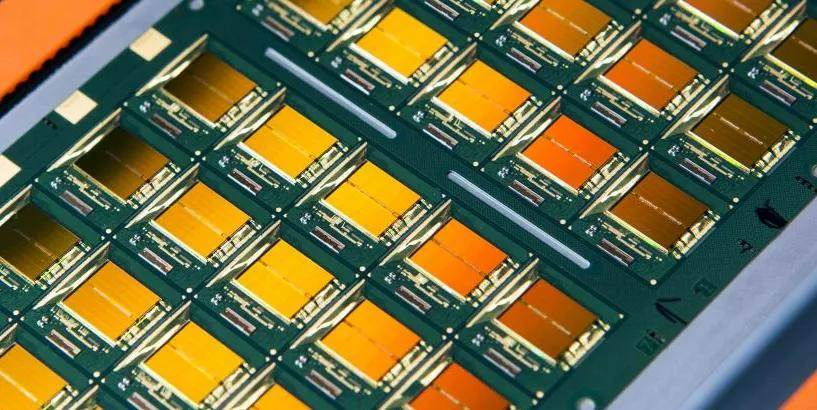

台积电2012年就开始量产CoWoS,通过该技术把多颗芯片封装到一起,通过Silicon Interposer高密度互连,达到了封装体积小,性能高、功耗低,引脚少的效果。

CoWoS技术应用很广泛,英伟达的GPU,谷歌的TPU都是采用CoWoS技术,人工智能AI的背后也有CoWoS的贡献。目前,CoWoS已经获得NVIDIA、AMD、Google、Apple、华为海思等几乎所有芯片厂商的大力支持。

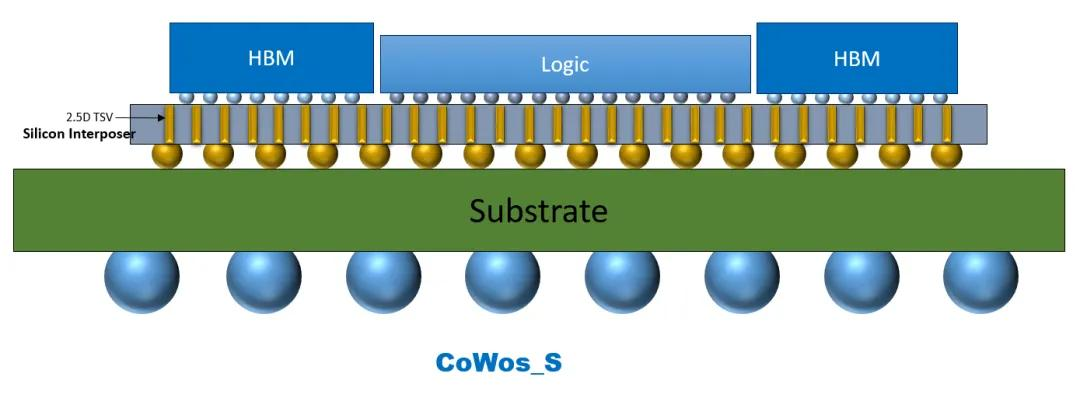

根据封装结构和工艺不同,CoWoS分为CoWoS-S,CoWoS-R,CoWoS-L,我们逐一进行解读。

CoWoS-S

CoWoS-S是带由硅中介层的

Chip-on-Wafer-on-Substrate,是传统的CoWoS工艺技术,该平台为人工智能(AI)和超级计算等超高性能计算应用提供了一流的封装技术。

CoWoS-S在大型Silicon Interposer区域上提供高密度互连和深沟槽电容器,以容纳各种功能性的管芯,包括Chiplet小芯片,在HBM(High Bandwidth Memory)领域有广泛的应用。目前支持高达3.3X掩模版尺寸(约2700mm2)的Silicon Interposer。

如果需要Interposer的尺寸大于3.3X掩模版尺寸。台积电则CoWoS-L和CoWoS-R,不同的选项提供了更灵活的集成,以满足各种性能和目标。

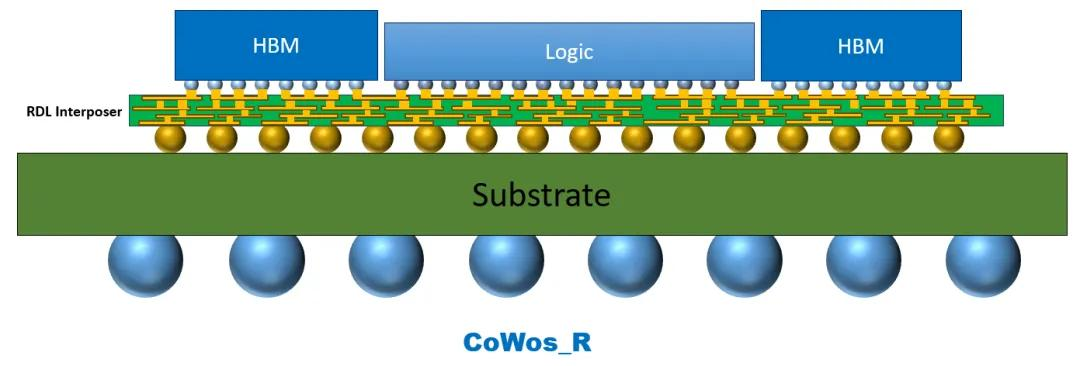

CoWoS-R

CoWoS-R是CoWoS先进封装家族的新成员,采用了InFO技术的RDL interposer服务于芯片之间的互连,可应用于HBM和Logic芯片的异构集成中。RDL插入层由聚合物和铜布线组成,具有相对Silicon interposer更好的机械柔性,并支持更大的interposer尺寸以满足更复杂的功能需求。

由此可见,CoWoS-R和CoWoS-S的区别在于interposer材料和工艺的不同,CoWoS-R采用了RDL interposer,类似于InFO中用到的互连技术。

CoWoS-R中的RDL interposer由6层铜组成,可支持2um线宽/间距。相比硅中介层的,RDL interposer的CTE和下部基板更为适配,RDL interposer和C4 Bump提供了良好的缓冲效果,应力和应变大大降低,从而提高了大面积中介层的可靠性。

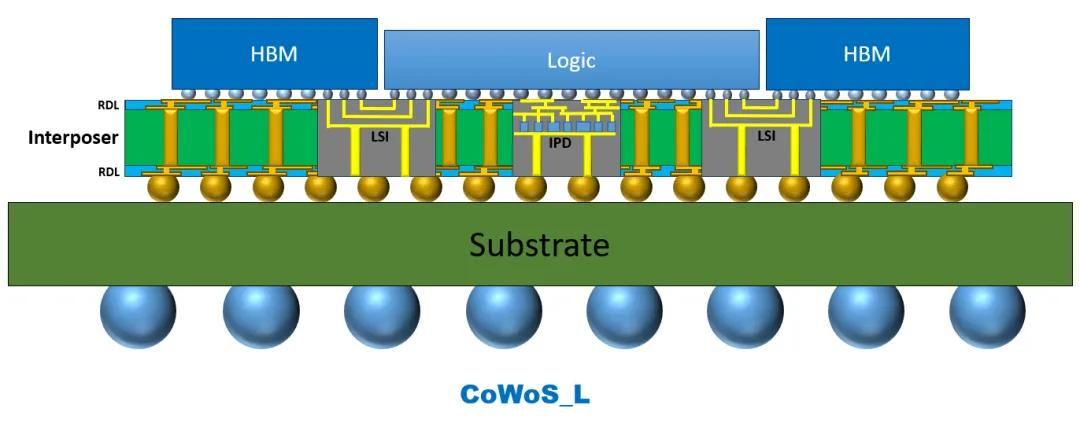

CoWoS-L

CoWoS-L结合了CoWoS-S和CoWoS-R的技术优点,使用中介层与局部硅互连LSI(Local Silicon Interconnect),为芯片提供了更加灵活的集成方式,其中RDL层用于电源和信号传输。该产品支持从1.5X掩模版尺寸开始,可扩展到更大的尺寸,以集成更多的芯片。

CoWoS-L的灵活性在于,对于布线密度非常高的区域,可采用LSI局部硅互连LSI支持多层亚微米铜线互连。LSI局部硅互连的金属类型、层数和间距与CoWoS-S的产品一致。

对于布线密度较为宽松的区域,则通过中介层和其表面的RDL层进行信号互连,CoWoS-L的中介层采用有机材质,在其正面和背面都有RDL层,穿过中介层的通孔连接正面和背面的RDL层,用于信号和功率的传输。

此外,CoWoS-L支持在逻辑芯片下方集成额外元件的能力,例如独立的IPD(集成无源器件),使其具有更好SI/PI性能。

从CoWoS的三种先进封装子类和特点,我们可以看出,CoWoS-S采用硅中介层,适合互连密度要求非常高的封装,其封装尺寸支持到MAX3.3X掩模版尺寸。CoWoS-R采用RDL中介层,可提供与基板之间良好的应力缓冲,封装尺寸支持大于3.3X掩模版尺寸。CoWoS-L采用混合中介层,支持局部硅互连和IPD无源器件,具有更高的灵活性,封装尺寸支持大于3.3X掩模版尺寸。

具体可根据项目的实际需求和预算进行灵活选用。

3 SoIC

SoIC也称为TSMC-SoIC,是台积电先进封装技术——集成片上系统(

System-on-Integrated-Chips)。

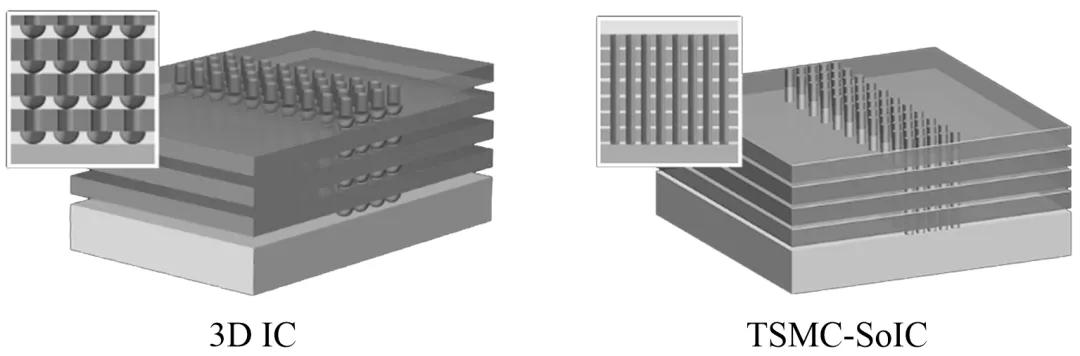

究竟什么是SoIC?所谓SoIC是一种创新的多芯片堆叠技术,能对10纳米以下的制程进行晶圆级的集成。该技术鲜明的特点是没有凸点(no-Bump)的键合结构,因此具有有更高的集成密度和更佳的性能。

SoIC包含CoW(Chip-on-wafer)和WoW(Wafer-on-wafer)两种技术形态,从TSMC的描述来看,SoIC是一种WoW晶圆对晶圆或CoW芯片对晶圆的直接键合(Bonding)技术。

下图是传统的3D IC和SoIC集成的比较。

具体的说,SoIC和3D IC的制程有些类似,SoIC的关键就在于实现没有凸点的接合结构,并且其TSV的密度也比传统的3D IC密度更高,直接通过极微小的TSV来实现多层芯片之间的互联。如上图所示是3D IC和SoIC两者中TSV密度和Bump尺寸的比较。可以看出,SoIC的TSV密度要远远高于3D IC,同时其芯片间的互连也采用no-Bump的直接键合技术,芯片间距更小,集成密度更高,因而其产品也比传统的3D IC有更高的功能密度。

CoW

CoW,Chip-on-Wafer

首先,将KGD(Known Good Die)芯片从晶圆上分离出来,并通过专用工具将KGD独立附着到基础晶圆上进行键合。

更常用的方式是,KGD对齐并首先临时粘合到重构的载体晶圆上,然后将载体晶圆键合到基础晶圆上以进行实际的预键合。顶部和底部芯片都是从原始硅晶圆上切割而成,并且对KGD进行分类。两组芯片都粘合到各自载体上的位置上。然后,通过WoW相同的工艺键合2个承载晶圆。

SoIC是将多个芯片采用混合键合的方式组装到一起,体积和性能上达到了单颗SoC同等的指标。

对比下图的SoC和SoIC,我们可以看出,SoIC至少有两个优势,1)异构集成,2)更高的功能密度。

SoIC-1,SoIC-2,SoIC-2可以采用不同的工艺节点生产,然后通过混合键合组装,支持异构集成,因此具有更高的灵活性。此外,SoIC具备更多的晶体管层,下图中,我用高亮标识出了晶体管层,可以看出,下图中SoC具有一个晶体管层,而SoIC具有两个晶体管层,在同样的工艺条件下,SoIC相比同体积SoC的具有两倍的晶体管数量,因此其功能密度也为SoC的两倍。随着堆叠层数的增多,这种优势会更加明显。

WoW

WoW(Wafer-on-wafer)

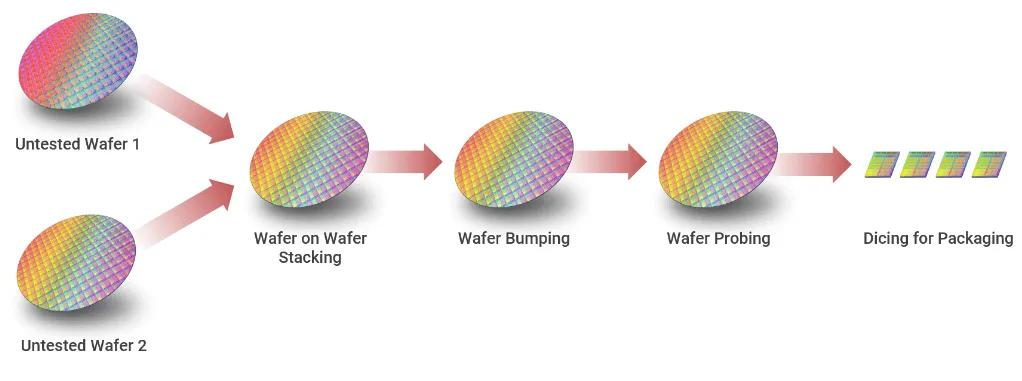

WoW是将两个或者多个制造好的晶圆直接键合在一起。WoW提供更高的对准精度、键合良率和更高的生产效率。鉴于这些优点,目前绝大多数混合键合都是通过WoW完成的。

WoW的生产流程大致如下,首先将晶圆堆叠并键合到一起,随后给底部晶圆植球,然后进行晶圆测试,进行分片和封装。

WoW键合的一个主要限制是无法选择已知良好的芯片(KGD)。这会导致将有缺陷的芯片粘合到良好的芯片上,或者良好的芯片粘合到有缺陷的芯片上,从而导致良好芯片的浪费。

因此,WoW适合良率高的晶圆,芯片尺寸较小时,WoW更便宜,更适合。然而,随着芯片尺寸的加大,每个晶圆上的良好芯片比例会减少,从而导致有缺陷的芯片和良好芯片的接合更多。

因此,需要结合WoW和CoW两种方式,对芯片尺寸较小,良率高的晶圆,采用WoW,对于对芯片尺寸大,良率低的晶圆,宜采用CoW

SoIC是台积电先进封装技术,和芯片制造高度融合,被台积电寄予厚望,也受到业界的高度关注。

相比SoC,SoIC具有更高的功能密度,并且支持异构集成,有着更高的集成灵活度,在未来必将成为芯片生产加工的常态,并取代SoC。